- 您现在的位置:买卖IC网 > Sheet目录3887 > PIC16F871-E/L (Microchip Technology)IC MCU CMOS 20MHZ 2K FLSH 44PLCC

PIC16F870/871

DS30569B-page 76

2003 Microchip Technology Inc.

9.4

USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode

in the fact that the shift clock is supplied externally at

the RC6/TX/CK pin (instead of being supplied internally

in Master mode). This allows the device to transfer or

receive data while in SLEEP mode. Slave mode is

entered by clearing bit CSRC (TXSTA<7>).

9.4.1

USART SYNCHRONOUS SLAVE

TRANSMIT

The operation of the Synchronous Master and Slave

modes is identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the

SLEEP

instruction is executed, the following will occur:

a)

The first word will immediately transfer to the

TSR register and transmit.

b)

The second word will remain in TXREG register.

c)

Flag bit TXIF will not be set.

d)

When the first word has been shifted out of TSR,

the TXREG register will transfer the second word

to the TSR and flag bit TXIF will now be set.

e)

If enable bit TXIE is set, the interrupt will wake

the chip from SLEEP and if the global interrupt

is enabled, the program will branch to the

interrupt vector (0004h).

When setting up a Synchronous Slave Transmission,

follow these steps:

1.

Enable the synchronous slave serial port by set-

ting bits SYNC and SPEN and clearing bit

CSRC.

2.

Clear bits CREN and SREN.

3.

If interrupts are desired, then set enable bit

TXIE.

4.

If 9-bit transmission is desired, then set bit TX9.

5.

Enable the transmission by setting enable bit

TXEN.

6.

If 9-bit transmission is selected, the ninth bit

should be loaded in bit TX9D.

7.

Start transmission by loading data to the TXREG

register.

8.

If using interrupts, ensure that GIE and PEIE

(bits 7 and 6) of the INTCON register are set.

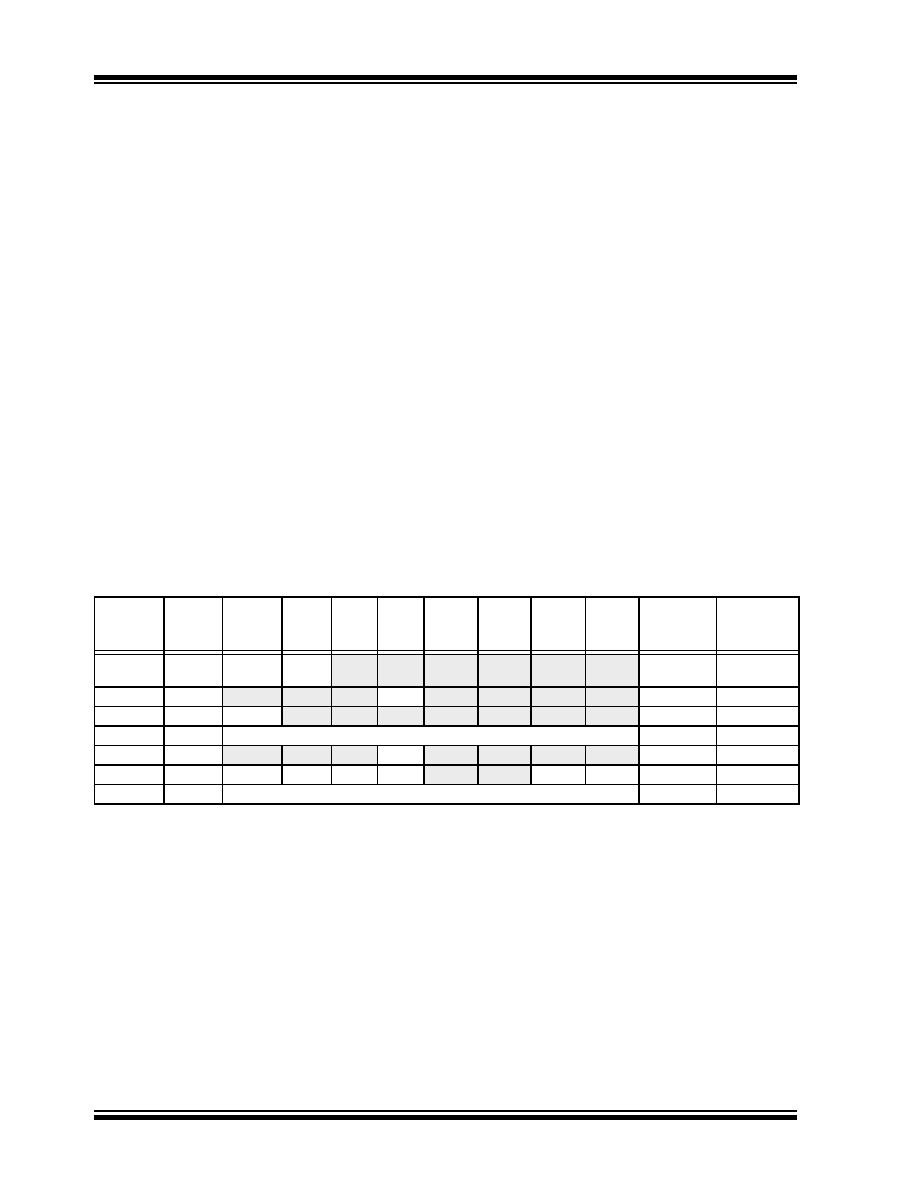

TABLE 9-10:

REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on:

POR, BOR

Value on

all other

RESETS

0Bh, 8Bh,

10Bh,18Bh

INTCON

GIE

PEIE

T0IE

INTE

RBIE

T0IF

INTF

R0IF

0000 000x

0000 000u

0Ch

PIR1

PSPIF(1)

ADIF

RCIF

TXIF

—

CCP1IF TMR2IF TMR1IF 0000 -000

0000 -000

18h

RCSTA

SPEN

RX9

SREN

CREN

ADDEN

FERR

OERR

RX9D

0000 000x

19h

TXREG

USART Transmit Register

0000 0000

8Ch

PIE1

PSPIE(1)

ADIE

RCIE

TXIE

—

CCP1IE TMR2IE TMR1IE 0000 -000

0000 -000

98h

TXSTA

CSRC

TX9

TXEN

SYNC

—

BRGH

TRMT

TX9D

0000 -010

99h

SPBRG

Baud Rate Generator Register

0000 0000

Legend:

x

= unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note

1:

Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F870T-E/SS

IC MCU CMOS 20MHZ 2K FLSH 28SSOP

PIC16F870T-E/SO

IC MCU CMOS 20MHZ 2K FLSH 28SOIC

PIC16F84AT-20E/SS

IC MCU CMOS 20MHZ 1K FLSH 20SSOP

PIC16F84AT-20E/SO

IC MCU CMOS 20MHZ 1K FLSH 18SOIC

22-15-3133

CONN FFC/FPC 13POS .100 RT ANG

PIC16F84AT-04E/SS

IC MCU CMOS 4MHZ 1K FLASH 20SSOP

22-02-3133

CONN FFC/FPC VERTICAL 13POS .100

PIC16F84AT-04E/SO

IC MCU CMOS 4MHZ 1K FLASH 18SOIC

相关代理商/技术参数

PIC16F871-E/P

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F871-E/PT

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F871-I/L

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F871-I/L

制造商:Microchip Technology Inc 功能描述:8BIT FLASH MCU SMD 16F871 PLCC44

PIC16F871-I/P

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F871-I/P

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 16F871 DIP40

PIC16F871-I/PT

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F871-I/PT

制造商:Microchip Technology Inc 功能描述:8BIT FLASH MCU SMD 16F871 TQFP44